## P-Channel 60-V (D-S) MOSFET

These miniature surface mount MOSFETs utilize a high cell density trench process to provide low  $r_{DS(on)}$  and to ensure minimal power loss and heat dissipation. Typical applications are DC-DC converters and power management in portable and battery-powered products such as computers, printers, PCMCIA cards, cellular and cordless telephones.

- Low r<sub>DS(on)</sub> provides higher efficiency and extends battery life

- Low thermal impedance copper leadframe DPAK saves board space

- Fast switching speed

- High performance trench technology

| PRODUCT SUMMARY            |                               |    |  |  |

|----------------------------|-------------------------------|----|--|--|

| <b>V</b> <sub>DS</sub> (V) | $r_{DS(on)} m(\Omega) = I_D($ |    |  |  |

| -60                        | $135 @V_{CS} = -10V$          | 16 |  |  |

|                            | $190@V_{C8} = -4.5V$          | 14 |  |  |

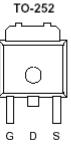

Top View

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25 °C UNLESS OTHERWISE NOTED) |                   |                 |            |       |  |

|--------------------------------------------------------------------------|-------------------|-----------------|------------|-------|--|

| Parameter                                                                |                   |                 | Maximum    | Units |  |

| Drain-Source Voltage                                                     |                   | VDS             | -60        | V     |  |

| Cate-Source Voltage                                                      |                   | Vas             | ±20        | V     |  |

| Continuous Drain Current <sup>a</sup>                                    | $T_A=25^{\circ}C$ | I <sub>D</sub>  | 16         | A     |  |

| Pulsed Drain Current <sup>b</sup>                                        |                   | I <sub>DM</sub> | ±40        | A     |  |

| Continuous Source Current (Diode Conduction) <sup>a</sup>                |                   |                 | -15        | Α     |  |

| Power Dissipation <sup>a</sup> T <sub>A</sub> =25°C                      |                   | PD              | 50         | W     |  |

| Operating Junction and Storage Temperature Range                         |                   |                 | -55 to 175 | °C    |  |

| THERMAL RESISTANCE RATINGS               |                 |         |       |  |  |

|------------------------------------------|-----------------|---------|-------|--|--|

| Parameter                                | Symbol          | Maximum | Units |  |  |

| Maximum Junction-to-Ambient <sup>a</sup> | $R_{\theta JA}$ | 50      | °C/W  |  |  |

| Maximum Junction-to-Case                 | $R_{\theta JC}$ | 3.0     | °C/W  |  |  |

Notes

a. Surface Mounted on 1" x 1" FR4 Board.

b. Pulse width limited by maximum junction temperature

| Parameter                               | Sympol         | Test Cost Ridson                                                            | Limits |     |      | TL.ª4 |

|-----------------------------------------|----------------|-----------------------------------------------------------------------------|--------|-----|------|-------|

| Faraneter                               | Symbol         | Test Conditions                                                             |        | Тур | Max  | Unit  |

| Static                                  |                |                                                                             |        |     |      |       |

| Gate-Threshold Voltage                  | VGS(th)        | $V_{DS} = V_{GS}$ , $I_D = -250 \text{ uA}$                                 | -1     |     |      |       |

| Gate-Body Leakage                       | Igss           | $V_{DS} = 0 V, V_{GS} = \pm 20 V$                                           |        |     | ±100 | nA    |

| Zero Gate Voltage Drain Current         | IDSS           | $V_{DS} = -48 V$ , $V_{GS} = 0 V$                                           |        |     | -1   | uA    |

|                                         | IDSS           | $V_{DS} = -48 \text{ V}, V_{GS} = 0 \text{ V}, T_J = 55^{\circ}\text{C}$    |        |     | -10  |       |

| On-State Drain Current <sup>A</sup>     | ID(on)         | $V_{DS} = -5 V$ , $V_{GS} = -10 V$                                          | -20    |     |      | Α     |

|                                         |                | $V_{GS}$ = -10 V, $I_D$ = -28 A                                             |        |     | 135  | mΩ    |

| Drain-Source On-Resistance <sup>A</sup> | IDS(on)        | $V_{GS} = -4.5 V$ , $I_D = -14 A$                                           |        |     | 190  |       |

| Forward Tranconductance <sup>A</sup>    | gś             | $V_{DS}$ = -15 V, $I_D$ = -28 A                                             |        | 8   |      | S     |

| Diode Forward Voltage                   | Vsd            | $I_{\rm S}$ =-2.5 A, $V_{\rm GS}$ =0 V                                      |        |     | -1.2 | V     |

| <b>Dynamic</b> <sup>b</sup>             |                |                                                                             |        |     |      |       |

| Total Gate Charge                       | Qg             | $V_{DS} = -30 \text{ V}, V_{GS} = -4.5 \text{ V},$<br>$I_D = -28 \text{ A}$ |        | 18  |      | nC    |

| Gate-Source Charge                      | Qgs            |                                                                             |        | 5   |      |       |

| Gate-Drain Charge                       | Qgd            |                                                                             |        | 2   |      |       |

| Tum-On Delay Time                       | td(on)         |                                                                             |        | 8   |      |       |

| Rise Time                               | tr             |                                                                             |        | 10  |      | nS    |

| Turn-Off Delay Time                     | td(off)        |                                                                             |        | 35  |      |       |

| Fall-Time                               | t <sub>f</sub> |                                                                             |        | 12  |      |       |

Notes

- Pulse test:  $PW \le 300$ us duty cycle  $\le 2\%$ . a.

- Guaranteed by design, not subject to production testing. b.